# During the second year of activities, the Consortium has made important progresses in several technical Work Packages (WPs).

### WP2 - Design of a silicon Root-of-Trust

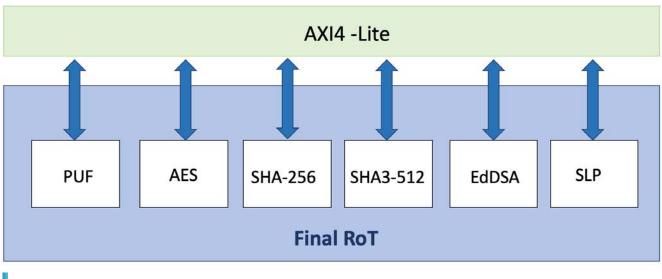

#### The final RoT in SPIRS is composed of the following hardware components (see Figure 1):

• **PUF**: a new version of the PUF module (PUFv2.2) that provides an area optimized implementation and a higher output bit rate. Additionally, the internal strategy for the challenge generation avoids the repetition of a challenge to obfuscate information against Electromagnetic Side-Channel Attacks (EM SCAs).

• AES: a new version of the module that combines hardware countermeasures, signature generator for Fault-Injection Attacks and Low-Entropy Masking Scheme (LEMS) for SCA.

• **SHA-256**: the hash function with 256 output bits of the SHA-2 family is chosen since it was demanded by some partners to be used in the development of their trusted applications. An enhanced hardware implementation in terms of area and timing performance is provided.

• SHA3-512: the hash function with 512 output bits of the SHA-3 family is chosen as alternative for partners that have required SHA-3 as hashing.

• EdDSA: an IP module to implement on hardware critical tasks in the digital signature scheme based on curve Ed25519.

• SLP: an IP module to detect fault-injection attacks due to extreme values of supply voltage and/or temperature, as well as malicious manipulations of clock and control signals at the system level.

Figure 1: Final RoT in SPIRS

In order to show the right functionality of the various RoT components resulting from their interconnection with a processing system, a demo has been developed. The demo has been implemented on Pynq-Z2 and Genesys 2 development boards

Follow us

### WP3 - Design of a Trusted Execution Environment

# In the context of WP3, demonstrators built on top of the second prototype of the SPIRS Trusted Execution Environment (TEE) have been developed:

- A firmware Trusted Platform Module (TPM) (fTPM) rooted in the core of the platform.

- The feasibility of integrating third party cryptography libraries like libgroupsig and OpenSSL into Trusted Applications (TAs).

#### Trusted Execution Environment

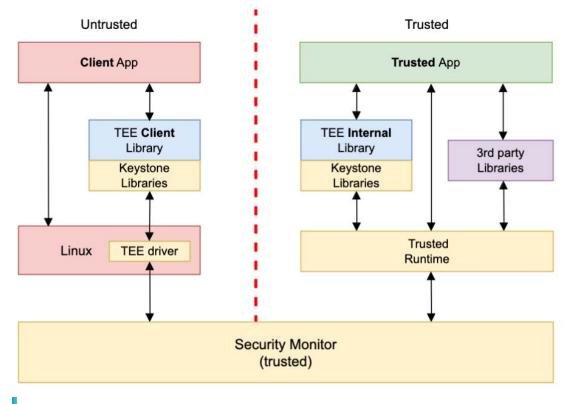

SPIRS TEE is based on the <u>Keystone</u> framework. Keystone is an open-source project for designing customized TEEs for RISC-V CPUs. This framework provides a TEE full-stack development environment that glues all the required components for instantiating or designing a TEE.

Figure 2 shows the software components of the platform. This figure includes Keystone (yellow) and SPIRS (blue) elements. The SPIRS components represent the implementation of GlobalPlatform TEE APIs on both the untrusted and trusted domains of the platform.

Figure 2: Basic SPIRS software stack

#### Secure and Measured Boot

In order to create a platform whose trustworthiness can be ensured and demonstrated, the SPIRS platform needs to include capabilities that allow Remote Attestation (RA) protocols to be enabled for all its components, hardware and software, starting from the boot up to the runtime phase. This was achieved in two steps: first of all, Secure and Measured Boot procedures were defined to ensure that the SPIRS platform booted in a trusted way; then, RA protocols were designed and implemented for all components of the SPIRS platform.

The SPIRS Project has received funding from the European Union's Horizon 2020 research and innovation programme under the Grant Agreement N° 952622

**Follow us**

Secure and Measured Boot procedures need a hardware anchor upon which to base trust in the platform. In SPIRS, the device identity is the Physical Unclonable Function (PUF) resident in the hardware RoT.

The SPIRS platform is equipped with the minimum set of elements that enable Secure, Measured Boot, and RA protocols, according to the Trusting Computing Group (TCG):

- the bootrom, which will contain the first measurement procedure, thus implementing the Root of Trust for Measurement (RTM);

- the PUF, capable of giving a statistically unique identity to the device, thus implementing the Root of Trust for Reporting (RTR);

- the Physical Memory Protection (PMP) extension defined in the RISC-V standard, which allows the creation of protected memory regions within which to store measurements, thus enabling Root of Trust for Storage (RTS).

#### Keystone based firmware Trusted Platform Module (TPM) (fTPM)

We leverage the SPIRS TEE to build an fTPM that can be used by the platform similarly to a discrete TPM. With this approach, it is expected that existing solutions that rely on a TPM device can be transparently and seamlessly used with an fTPM. One relevant example of this is the Linux IMA subsystem which uses a TPM if it is available in the platform.

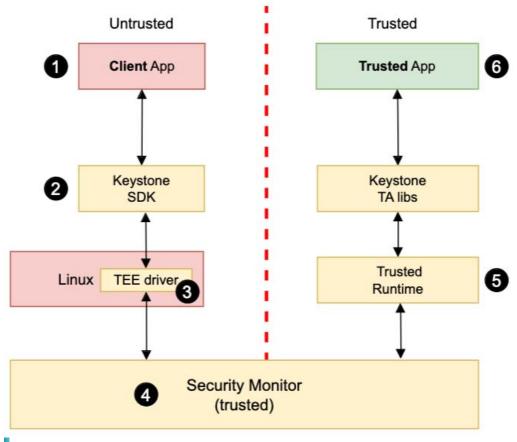

Keystone v1.0 heavily depends on Linux userspace to create a TA. The numbering in Figure 3 illustrates this process as a sequence, detailed as follows. The CA (1) initiates this procedure by using the Keystone SDK (2) libraries, which are wrappers for the Keystone TEE driver (3) in the Linux kernel. The Security Monitor (4) acts as a proxy between the security domains and creates the Trusted Runtime (5) in an isolated environment, and then finally executes the TA (6). At this point the CA and TA can exchange information using the Keystone SDK and Keystone TA libraries.

Figure 3: Keystone framework software stack

The SPIRS Project has received funding from the European Union's Horizon 2020 research and innovation programme under the Grant Agreement N° 952622

#### Group signatures schemes

A Privacy Enhancing Toolbox has been developed for such a goal, with the anonymization of users' or entities' identities as one of the functionalities of this toolbox. Two distinct group signature schemes have been selected:

- Traceable group signatures defined by Kiayias, Tsionis and Yung (KTYO4) that rely on RSA and discrete logarithm assumptions

- Group signatures defined by Pointcheval and Sanders (PS16) that are based on bilinear pairings.

The selected library can be downloaded here that is is an improved version of libgroupsig.

### WP4 - Integration into network infrastructures

Network integration features:

- JOINT Orchestration, Management and Control of 5G System and Trusted Applications on heterogeneous types of TEE-enabled TNEDs

- EXTENSIBLE Controller Architecture through OpenAPIs integrates features of Resources- and Lifecycle Management, Application Deployment and Attestation in REE & TEE, and TA Configuration

- AUDITABLE procedure and compliance checks through logging

- PROTECTED END-TO-END COMMUNICATION through IPsec Overlay

Validation:

|                                                                                                           | 2                                           | 3                                                                                                                          | 4                                                                                                  |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| From Edge Control to Trust                                                                                | Distributed Attestation                     | Centrally Controlled IPsec                                                                                                 | Group Signatures                                                                                   |

| Control                                                                                                   | Remote attestation of                       | (CCIPS)                                                                                                                    | Shows the functionality supported                                                                  |

| Orchestration and Life-Cycle<br>Management of Applications<br>on sliced RISC-V edge platform<br>resources | computational entities<br>deployed on TNEDs | Management of IPsec tunnels in a 5G<br>network protecting the communication<br>and data treated by Trusted<br>Applications | by the group signature library,<br>that will be used to implement<br>privacy respectful AAAA proto |

#### 4 available demos:

| 1               | 2                  | 3                     | 4                |

|-----------------|--------------------|-----------------------|------------------|

| Demonstrate     | Demonstrate        | Demonstrate           | Fully functional |

| first evolution | first evolution of | enhanced 5G           | KTY04 group      |

| of the Edge     | remote             | network security      | signature        |

| Controller for  | attestation        | by leveraging         | scheme in the    |

| orchestration   | protocols for      | CCIPS,                | TEE              |

| of Kubernetes   | containerized      | secure                |                  |

| container       | workloads          | configuration         |                  |

| virtualization  | deployed on        | handling, and         |                  |

| on a RISC-V     | MNO Edge           | protection of         |                  |

| edge resource   | System             | cryptographic<br>data |                  |

The SPIRS Project has received funding from the European Union's Horizon 2020 research and innovation programme under the Grant Agreement N° 952622

Follow us

### WP5 - Platform integration

A preliminary FPGA implementation of the SPIRS platform has been developed:

| 1 To assess the correct<br>functionality of the<br>SPIRS platform<br>integrating a secure | <b>2</b> To characterize the performance of the platform: | <b>3</b> To implement a preliminary SPIRS platform on FPGA |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|

| CVA6-based<br>processor (SPRITZ)                                                          | <ul> <li>Area occupation</li> </ul>                       | <ul> <li>HW/SW<br/>components</li> </ul>                   |

| and RoT components developed in WP2                                                       | <ul> <li>Power consumption</li> </ul>                     | integration and validation                                 |

### Features of the SPIRS plataform:

|  | <b>2</b><br>Fully compliant with Compliant with                      |                                | INTERFACE<br>REQUIREMENTS                                                                                           | DESCRIPTION                                                          | INTEGRATION<br>STATUS |

|--|----------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------|

|  | "System Requirements"<br>described in the D3.1<br>deliverable<br>T   | Serial Interface<br>(UART)     | Serial Interface to connect to the<br>machine controller and retrieve/send<br>data from/to                          | Complete                                                             |                       |

|  |                                                                      | Serial Interface<br>(User USB) | (Customer Side) Upload the firmware<br>on the SPIRS Platform before securely<br>transferring it to the manufacturer | Work-in-progress                                                     |                       |

|  | ə<br>ALL IP modules are                                              | <b>4</b><br>ALL IP modules use | Ethernet                                                                                                            | Network communication                                                | Complete              |

|  | memory mapped to a<br>processor compatible with<br>RISC-V RV64GC ISA | a AXI4-compliant               | User interaction<br>(USB HID)                                                                                       | User inputs                                                          | Work-in-progress      |

|  |                                                                      | interface                      | User feedbacks<br>(HDMI or VGA)                                                                                     | Feedbacks on specific actions (e.g.,<br>operation started/completed) | Work-in-progress      |

### Verification of the SPIRS platform:

Follow us

(in

### Demo of the SPIRS platform:

A preliminary version of the SPIRS platform integrating SPRITZ

A design flow to implement the platform on the project reference FPGA development board (Genesys 2) An environment to build SW running on the HW platform

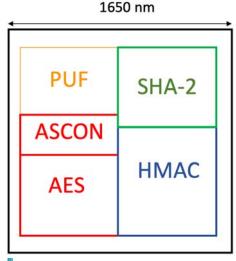

# First VLSI integration of a lightweight Root-of-Trust (RoT)

A 3.57 mm2 ASIC has been taped out for integration in TSMC 65nm technology:

• to assess the viability of designing building blocks in dedicated hardware;

• to enable higher integration, with less power consumption and reduced hardware resources, yielding a lightweight version of a RoT to be used in constrained scenarios where security is a must.

3

Figure 4: Distribution of the blocks in the ASIC

### WP7 - Dissemination and exploitation of results

2

A summary of dissemination activities in numbers (first and second year):

- 8 publications in peer-reviewed international journals

- 22 participations in peer-reviewed conferences

- 12 talks in seminars and webinars

- 1 whitepaper

Communicating and promoting SPIRS (first and second year):

- 6 promotional videos

- 7 participations in outreach activities for general audience

- Active participation in social media

- 1 whitepaper

The SPIRS Project has received funding from the European Union's Horizon 2020 research and innovation programme under the Grant Agreement N° 952622

| •••••••                | <u> </u>                      |            |

|------------------------|-------------------------------|------------|

| Description            | How?                          | When?      |

| Intermediate meeting   | Hybrid - Heidelberg (Germany) | March 2023 |

| First Reporting Period | Hybrid – Seville (Spain)      | June 2023  |

### SPIRS consortium meetings for 2nd year

SPIRS meeting in Heidelberg (March 2023)

First review in SPIRS (June 2023)

The SPIRS Project has received funding from the European Union's Horizon 2020 research and innovation programme under the Grant Agreement N° 952622

Follow us lacksquare

in